Abstract

Advent in VLSI technology made digital signal processing to take over analog signal processing. Analog to digital converter plays a vital role in modern digital signal processing applications. Various signal processing applications incorporated sigma delta ADC among different analog to digital converters because of its digital dominant architecture. This paper presents the design of a low pass continuous time sigma delta analog to digital converter on-chip architecture with a very few passive components connected externally to FPGA suitable for signal processing applications, wireless application, sonar and radar beamforming. Schematic level architecture of high speed comparator working at a differential swing which is not allowed by FPGA standard differential pads is designed. By applying various differential swings at the input to LVPECL, the performance and power is analyzed. High performance comparator schematic is designed as on-chip continuous-time sigma-delta analog to digital converter architecture. SPICE simulations are carried out to verify the maximum input frequency for given RC values. Xilinx provided Spartan 6 I/O pad and package SPICE models are used. Power analysis is carried out with LVPECL logic family based differential buffers along with external RC circuit. The analog and digital sections simulations along with mixed signal simulations at different stages are performed. Power and performance analysis are carried out using h-Spice and questasim simulations. schematic level architecture of a high speed comparator at a differential swing of 1.65 ± 1.5 V which is not allowed by standard differential pads is designed. Analysis illustrates that proposed on-chip continuous-time sigma-delta analog to digital converter exhibits a sampling rate of 400 MHz designed with high speed comparator with varied differential swing. Power analysis resulted with 1.86 mW for an input signal of 1 MHz. Optimal filtering is achieved with total decimation of 400, out of which the decimation of 100 is achieved by CIC filter and PFIR filter achieves remaining decimation factor of 4. Output data rate of 1 MHz with a dynamic range of 72 dB is achieved with less bill of material that suites for signal processing applications.

Similar content being viewed by others

1 Introduction

Signal processing represents, transforms, and manipulates a signal and the signal information. Signal processing technology used before 1960s was Continuous Time (CT) analog technology. But noise comes into existence in processing a signal using analog technology. Signal processing on analog circuits are even complex. But the advancement in IC technology, digital signal processing took over analog processing. The processing of signal in digital system is done using digital computation. In contrast to analog systems, the digital systems provide better reliability and resolution at a low cost. Digital systems became area efficient circuits with growth of silicon technology. Digital systems are less susceptible to noise and they add an additional feature of programmability (Brandt 1991).

Evolution of Very Large Scale Integration (VLSI) circuits led to the implementation of high performance and high resolution architectures. Digital signal processing system found its application in every field of daily life viz., consumer electronics, industrial applications, speech synthesis. Digital signal processing systems need the real-time occurring signals to be converted into digital form for processing and vice versa to get the analog output from digital processing system. Hence data converters, Analog to Digital Converters (ADCs) and Digital to Analog Converters (DACs) are required to interface the real-time analog world and the digital processing systems as in Fig. 1. Interfacing the digital domain with the analog world became the bottleneck for the designers for the processing system as lot of filtering circuits, complex conversion procedures, noise rejection and elimination circuits are involved.

1.1 Need for sigma delta ADC digital architecture

ADCs perform the conversion of analog to digital by different methods. By 1960s, new architectures aroused with the replacement of vacuum tubes by transistor and later by IC technology. Among various Nyquist ADCs, parallel or flash ADC is known for its high speed, Successive approximation ADC gives better accuracy but at moderate speeds. Oversampling ADCs trade digital signal processing complexity for relaxed requirements on the analog components compared to Nyquist rate ADCs. Oversampling ADCs or sigma delta architecture based on oversampling and noise shaping principles monopolized most of the applications in the last two decades (Norsworthy et al. 1996; Jacomet et al. 2004). The approach earlier by the VLSI researchers is towards Application Specific Integrated Circuit (ASIC) implementation and the analog VLSI synthesis is not automated. Research in the direction of digital implementation of the ADC is being carried out (Harsha Vardhini et al. 2012). Field Programmable Gate Array (FPGA) implementations of sigma delta ADC competed with the ASIC implementations evolving new architectures.

ASIC and FPGA implementations of sigma delta architectures allows the designers in realizing an ADC delivering reasonably good performance. But both implementations presented various limitations. Some of them are listed below.

-

Utilization of the silicon by the ADCs.

-

As the converters are placed outside the processing system they require an interface, like SPI, I2C, etc., to get connected with processing system

-

Protocol is to be followed for interfacing

-

Synchronization in multi channel ADC applications

Artigas et al. (2009) research proposed with active component digital only SD-ADC for the digitization of the parameters related to the power supply describing the dynamic comparator analysis that is carried out by implementing the negative feedback around the inverter. However, in practical FPGA circuits, possible threshold level variations of inverter gate with temperature, ageing etc. are not considered. Such unpredictable variations degrade the overall output of modulators. In low Vdd and high velocity switches these differences become more important. In addition, an FPGA input pad is used as a comparator, the hysteresis of which may produce unwanted device poles which may cause errors in the operation of signal and noise transfer (Sousa et al. 2004). The research in Palagiri et al. (2012) emphasizes the use of an LVDS input buffer as comparator on another all digital implementation. In the context of passive analog and FPGA/ASIC based SD-ADC, Jacomet et al., Fabio Sousa et al., and Artigas works are surveyed and the work proposed here describes the simulation of passive analog only SD-ADC with two high speed differential pins in Xilinx Spartan and Virtex family FPGAs. FPGA differential I/Os perform as 1 bit comparator and the digital analysis of the same can be done with spice simulations (Artigas et al. 2009; Sousa et al. 2004). FPGA configurable logic blocks can be programmed to achieve the digital block modules that perform the operation of filtering and decimation (Palagiri et al. 2012). 7 series FPGAs like ZYNQ, PYNQ with AMS technology is the motivation for the present research in the upcoming mixed signal IP technologies that provide flexibility for general purpose analog interface (Harsha Vardhini et al. 2013; Palagiri et al. 2013b).

Xilinx FPGAs are chosen due to the availability of software and tools for the simulation. However, the methodologies presented here are technology-independent, and can be applied to any FPGAs and ASIC category. The performance benchmarks are given with FPGAs made from 90 nm technology, widely used in today's systems. The approach presented in this paper presents the design of area and cost efficient sigma delta ADC with optimum performance. The second section illustrates the design of low-pass on-chip continuous-time sigma-delta ADC. Power analysis of differential I/O is carried out and tabulated in third section and fourth section illustrate the design of high speed comparator suitable for proposed architecture. The fifth section concludes the proposed work suitable for SONAR and many wireless communication applications.

2 Design of low-pass on-chip continuous-time sigma-delta ADC on FPGA

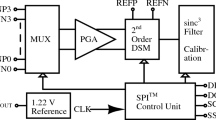

Proposed sigma delta ADC architecture suitable for signal processing applications is depicted in Fig. 2. It is a 12-bit high performance first order sigma delta ADC implemented on FPGA to overcome the limitations described in the above section.

This work makes use of Xilinx FPGA to design sigma delta ADC. Conventional ASIC sigma delta modulator block is implemented here in this work with LVPECL I/O of FPGA and a resistor R and capacitor C are placed outside which are connected to the I/O, represents first order CT sigma delta modulator. Digital section following the modulator for down conversion and decimation process is implemented by the Configurable Logic Blocks (CLBs) of FPGA.

2.1 Selection of R&C

The external RC product decides the maximum input frequency. Simulations are carried out to verify the maximum input frequency for given RC value. Resistor value R is fixed, as the impedance matching needs 100 Ω termination and C is varied.

The maximum input signal frequency for LVPECL differential I/Os with various capacitor values for different voltage swings are listed in following tables. Table 1 illustrates the maximum input frequency at a various differential swing with 1 pf capacitor. Tables 2 and 3 illustrates the maximum input frequency at various input swings for LVPECL I/O with a capacitor of 10 pf and 100 pf respectively. Table 4 tabulates the same for a capacitance of 1000 pf or 1 nf. From Fig. 3, it can be interpreted that LVPECL with higher clock speed is suitable for high speed applications.

3 Power analysis of LVPECL comparator

Conventional sigma delta ADC requires comparator with faster dynamic response and stable operating conditions. FPGA differential pins can be used as comparator. Xilinx FPGA families supports various differential I/O standards viz., Low Voltage Differential Signaling (LVDS), mini LVDS, Bus LVDS, High Speed Transceiver Logic (HSTL), Reduced Swing Differential Signaling (RSDS), Low Voltage Positive Emitter coupled Logic (LVPECL), Transition Minimized Differential Signaling (TMDS), Point-to-Point Differential signaling (PPDS), so on (Harsha Vardhini and Madhavi Latha 2015; Palagiri et al. 2013a). The selected FPGA is Spartan-6 family which supports several differential signal types. Among the differential I/Os LVPECL is selected due to their fast switching speeds. The analog part and the LVPECL differential I/O simulations are carried out with H-SPICE simulator. Xilinx provided Spartan 6 I/O pad and package SPICE models are used for this simulation (Vardhini 2016). By applying various differential swings at the input to LVPECL, the performance and power is analyzed. Differential I/Os h-spice simulations are carried out and the results are illustrated in Table 5. Power analysis is carried out with LVPECL logic family based differential buffers along with external RC circuit for realizing 1-bit sigma delta ADC. The results are tabulated below as in Table 6 and it reports less than 1.9 mW power, which is comparable with typical low power ADC requirements. Table 6 depicts that LVPECL works at a maximum clock speed of 200 MHz and it fails to operate at a higher frequency above 200 MHz. Figure 4 depicts the power and performance analysis of LVPECL, LVDS and HSTL-II differential I/Os.

4 Design of high speed comparator

Using a normal FPGA I/O, limits the swing of the applied input. nm-CMOS comparator with varied differential swing is designed. This section proposes a schematic level architecture of a high speed comparator which works at a differential swing of 1.65 ± 1.5 V which is not allowed by standard differential pads. For the future FPGAs this architecture can be implemented for high performance on-chip architecture. Comparator schematic as shown in Fig. 5 comprised of preamplifier, decision and output buffer stages. A D-flipflop and a digital buffer follow the comparator stage. Digital buffer ensure to produce the logic levels compatible to digital circuits. According to level 49 simulations, schematic extracted netlist of 130 nm model files are simulated and the results illustrate that this comparator works at 400 MHz clock.

4.1 CIC based decimator with 1-bit input at these high rates in digital fabrics

CIC architecture is as shown in Fig. 6 where by the down sampling by a factor of D is carried out by integrators before comb sections. A total decimation of 400 is achieved out of which the decimation of 100 is achieved by CIC filter and PFIR filter achieves remaining factor of 4. Proposed sigma delta ADC top level functionality is verified by Analog Mixed Signal VHDL. The analog and digital sections and mixed signal simulations at different stages are carried out and compared with the work contributed by Sousa et al. (2004) using FPGA I/O pads with LVDS as a comparator for SD-ADC in Table 7.

Power and performance analysis are carried out using h-Spice and questasim simulations. schematic level architecture of a high speed comparator at a differential swing of 1.65 ± 1.5 V which is not allowed by standard differential pads is designed. Analysis illustrates that proposed on-chip continuous-time sigma-delta analog to digital converter exhibits a sampling rate of 400 MHz designed with high speed comparator with varied differential swing. Power analysis resulted with 1.86 mW for input signal of 1 MHz with output data rate of is 1 MHz with a dynamic range of 72 dB.

4.2 Applications

On-chip sigma-delta ADC architecture with FPGA differential I/Os find its applications including low cost instrumentation, audio, SONAR and sensor networks. Among several applications the sigma delta ADC architectures are highly suitable for many wireless applications where ADC is a requisite and the count of ADCs needed by the application is more in number. Wireless applications, RADAR, SONAR applications can be easily benefitted with the proposed architecture due to the advantages over existing categories (Palagiri et al. 2016; Bindu Tushara and Harsha Vardhini 2015). Firstly, SONAR beamforming applications require digitization of SONAR signals coming from multiple sensors with high level of time synchronization. Multi channel inputs where analog to digital conversion is required can be replaced with proposed architecture (Bindu et al. 2017; Szczesny et al. 2020).

Secondly, for low cost wireless sensor networks, wireless transceivers infrastructure for industrial automation and sensor networks where analog to digital converters are extensively used in current and future automation topologies, there is a constant effort to evolve low cost wireless nodes (Hu et al. 2019; Harsha Vardhini and Murali Mohan Babu 2020). The proposed on-chip ADC is suitable for wireless transceivers with required bandwidth access. IoT based wireless applications implemented with arduino, raspberry pi or any controller boards with ‘n’ number of sensor and ADCs can be replaced with the proposed on-chip ADC FPGA architecture (Babu and Harsha Vardhini 2020; Harsha Vardhini et al. 2020; Vasishta et al. 2020).

5 Conclusion

On-chip sigma delta ADC with the Xilinx FPGA differential I/O i.e., LVPECL is analyzed and the on-chip architecture is simulated with the proposed comparator design. schematic level architecture of a high speed comparator at a differential swing of 1.65 ± 1.5 V which is not allowed by standard differential pads is designed. Analysis illustrates that proposed ADC exhibits a sampling rate of 400 MHz designed with high speed comparator with varied differential swing. Power analysis resulted 1.86 mW for input signal of 1 MHz. Optimal filtering is achieved with total decimation of 400, out of which the decimation of 100 is achieved by CIC filter and PFIR filter achieves decimation factor of 4. Output data rate of is 1 MHz with a dynamic range of 72 dB. SONAR/RADAR applications utilizing the maximum silicon area for analog to digital conversion of the real time signals can be easily achieved by replacing the proposed architecture with the existing FPGA architecture differential I/Os. Proposed On-chip sigma delta ADC design enable high end signal processing application realization with less bill of material.

References

Artigas, J. I., Urriza, I., Navarro, D., Barragan, L. A., & Acero, J. (2009). Comparator-less digital implementation of AC-coupled ΣΔ A/D converters. Electronics Letters, 45(11), 537–538.

Bindu Tushara, D., & Harsha Vardhini, P. A. (2015). FPGA implementation of image transformation techniques with Zigbee transmission to PC. International Journal of Applied Engineering Research, 10(55), 420–425.

Babu, K. M. C., & Harsha Vardhini, P. A. (2020). Design and development of cost effective arduino based object sorting system. In 2020 International conference on smart electronics and communication (ICOSEC), Trichy, India (pp. 913–918). https://doi.org/10.1109/ICOSEC49089.2020.9215269.

Bindu Tushara, D., & Harsha Vardhini P. A. (2017). Performance of efficient image transmission using Zigbee/I2C/Beagle board through FPGA. In H. Saini, R. Sayal, S. Rawat (Eds.), Innovations in computer science and engineering. Lecture notes in networks and systems (Vol. 8). Singapore: Springer. https://doi.org/10.1007/978-981-10-3818-1_27.

Brandt, B. P. (1991). Oversampled analog-to-digital conversion. Integrated Circuits Labaratory, Technical Report No. ICL91-009, Stanford University.

Harsha Vardhini, P. A., Harsha, M. S., Sai, P. N., & Srikanth, P. (2020). IoT based smart medicine assistive system for memory impairment patient. In 2020 12th international conference on computational intelligence and communication networks (CICN), Bhimtal, India (pp. 182–186). https://doi.org/10.1109/CICN49253.2020.9242562.

Harsha Vardhini, P. A., & Madhavi Latha, M. (2015). Power analysis of high performance FPGA low voltage differential I/Os for SD ADC architecture. International Journal of Applied Engineering Research, 10(55), 3287–3292.

Harsha Vardhini, P. A., Madhavi Latha, M., & Krishna Reddy, C. V. (2012). A 65 dB SF DR, 500 kS/s continuous time all digital sigma delta a DC for SON AR applications. In Pearl Jubilee international conference on “navigation and communication” (NAVCOM-2012).

HarshaVardhini, P. A., Madhavi Latha, M., & Krishna Reddy, C. V. (2013). Analysis on digital implementation of Sigma-Delta ADC with passive analog components. International Journal of Computing and Digital Systems (IJCDS), University of Bahrain, 2(2), 71–77.

Harsha Vardhini, P. A., & Murali Mohan Babu, Y. (2020). FPGA based energy-aware image compression and transmission with single board computers. Journal of Green Engineering, 10(5), 2483–2497.

Hu, J., Li, D., Liu, M., & Zhu, Z. (2019). A 10-Ks/s 625-Hz-bandwidth 65-db SNDR 2nd-order noise-shaping SAR ADC for biomedical sensor applications. IEEE Sensors Journal. https://doi.org/10.1109/jsen.2019.2949641.

Jacomet, M., Goethe, J., Zbinden, V., & Narvez, C. (2004). On the dynamic behavior of a novel digital-only sigma-delta A/D converter. In Proceedings of sympsoium on integrated circuits and system design, Pernambuco, Brazil (pp. 222–227).

Norsworthy, S. R., Schreier, R., & Temes, G. C. (1996). Delta-sigma data converters: Theory, design and simulation. New York: IEEE Press.

Palagiri, A. H. V., Makkena, M. L., & Chantigari, K. R. (2016). An efficient on-chip implementation of reconfigurable continuous time sigma delta ADC for digital beamforming applications. In Advances in Intelligent Systems and Computing (Vol. 381, pp. 291–299). https://doi.org/10.1007/978-81-322-2526-3_31.

Palagiri, H., Makkena, M., & Chantigari, K. R. (2013a). Design development & performance analysis of high speed comparator for reconfigurable ΣΔ ADC with 180 nm TSMC technology. In 15th International conference on advanced computing technologies (ICACT 2013).

Palagiri, H. V., Makkena, M. L., & Chantigari, K. R. (2012). Performance analysis of first order digital sigma delta ADC. In 2012 Fourth international conference on computational intelligence, communication systems and networks, Phuket (pp. 435–440). https://doi.org/10.1109/CICSyN.2012.84.

Palagiri, H. V., Makkena, M. L., & Chantigari, K. R. (2013b). Optimum decimation and filtering for reconfigurable sigma delta adc. Far East Journal of Electronics and Communications, 11(2), 101–111.

Sousa, F., Mauer, V., Duarte, N., Jasinski, R. P., & Pedroni, V. A. (2004). Taking advantage of LVDS input buffers to implement sigma-delta A/D converters in FPGAs. In Proceedings of international symposium on circuits and systems, Vancouver, BC, Canada (Vol. 1, pp. 1088–1091).

Szczesny, S., Kropidłowski, M., & Naumowicz, M. (2020). 0.5-V ultra-low-power modulator for sub-NA signal sensing in amperometry. IEEE Sensors Journal, 20(11), 5733–5740.

Vardhini, P. A. H. (2016). Analysis of integrator for continuous time Digital sigma Delta ADC on Xilinx FPGA. In International conference on electrical, electronics, and optimization techniques, ICEEOT 2016 (pp. 2689–2693).

Vasishta, S., Raghunandan, K. R., Dodabalapur, A., & Viswanathan, T. R. (2020). Level-crossing detection based low-power sigma-delta ADC for sensor applications. In 2020 IEEE 63rd international midwest symposium on circuits and systems (MWSCAS), Springfield, MA, USA (pp. 663–666). https://doi.org/10.1109/MWSCAS48704.2020.9184615.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

About this article

Cite this article

Vardhini, P.A.H., Makkena, M.L. Design and comparative analysis of on-chip sigma delta ADC for signal processing applications. Int J Speech Technol 24, 401–407 (2021). https://doi.org/10.1007/s10772-021-09800-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10772-021-09800-8